Arquitetura de hardware para criptografia pós-quântica

A integração de algoritmos de segurança pós-quântica ao hardware era anteriormente considerada um desafio. Uma equipe de pesquisa da Universidade de Tecnologia de Graz desenvolveu hardware padronizado com medidas de segurança adicionais.

Ainda não são uma realidade, mas num futuro não muito distante, computadores quânticos sofisticados e poderosos estarão disponíveis. Revolucionarão domínios como a inteligência artificial, a modelização financeira, o desenvolvimento de medicamentos, a previsão meteorológica e a otimização do tráfego, mas também representarão um risco no domínio da cibersegurança. Um poderoso computador quântico será capaz de quebrar vários algoritmos criptográficos essenciais para proteger o mundo digital. É por isso que vários algoritmos quânticos seguros já estão em desenvolvimento, conhecidos como algoritmos de criptografia pós-quântica (PQC). Contudo, implementá-los em dispositivos eletrônicos tem sido um problema até agora. No projeto PQC-SRC, uma equipe liderada por Sujoy Sinha Roy, do Instituto de Tecnologia Aplicada de Processamento de Informação e Comunicação (IAIK) da TU Graz, desenvolveu hardware para esses algoritmos e implementou medidas de segurança adicionais. Os pesquisadores também estiveram em contato com empresas como Intel e AMD.

Entre os algoritmos recentemente desenvolvidos, aqueles baseados em problemas computacionais com estruturas matemáticas de rede são considerados particularmente promissores. Resolver esses problemas computacionais também é considerado impossível para computadores quânticos. Como parte de sua padronização para criptografia pós-quântica, o Instituto Nacional de Padrões e Tecnologia (NIST) dos EUA selecionou um método de encapsulamento de chave (encapsulamento de chave baseado em rede ou KEM) chamado “Kyber” e três algoritmos de assinatura digital, ” Dilithium”, “Falcon” e “SPHINCS+”, que foi co-desenvolvido no IAIK. Os algoritmos KEM permitem que duas partes em comunicação cheguem a um acordo seguro sobre uma chave secreta. Os algoritmos de assinatura digital permitem que um destinatário verifique a autenticidade das mensagens recebidas.

Necessidade de um design seguro e eficiente

Após o anúncio dos algoritmos padronizados, as organizações, as empresas e a indústria estão se preparando para a transição para a criptografia quântica segura. Isso significa que todos os dispositivos devem ser convertidos do KEM clássico e dos procedimentos de assinatura para seus equivalentes pós-quânticos. É, portanto, necessário que os algoritmos recentemente padronizados possam ser usados na mais ampla gama possível de dispositivos eletrônicos.

Para tornar a transição para a criptografia quântica segura o mais livre de problemas possível, são necessários métodos de design e implementação seguros e eficientes. Os pesquisadores da Equipe de Engenharia Criptográfica liderada por Sujoy Sinha Roy do IAIK desenvolveram tais métodos, prestando especial atenção aos dispositivos eletrônicos com poucos recursos.

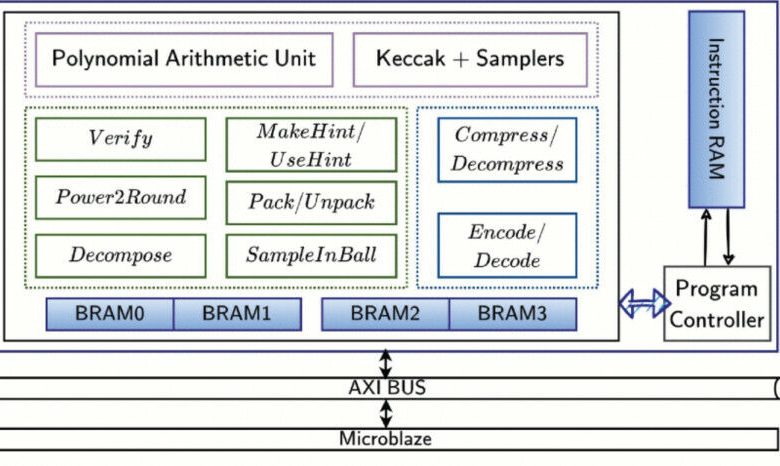

Desenvolvimento de um coprocessador baseado em hardware para criptografia pós-quântica padronizada

Um resultado desta pesquisa é a construção de um coprocessador criptográfico padronizado denominado “KaLi”, que suporta tanto o método de encapsulamento de chave “Kyber” quanto o algoritmo de assinatura digital “Dilithium”. Esse design unificado é essencial para protocolos de comunicação seguros, como o amplamente utilizado Transport Layer Security (TLS), que utiliza encapsulamento de chaves e assinaturas digitais. Um dos maiores desafios durante o desenvolvimento foi manter o design do coprocessador compacto, pois os algoritmos requerem mais memória e unidades de computação do que a criptografia convencional. Se o design não atender a esses requisitos de eficiência, muitos dispositivos com recursos limitados, como aplicativos de cartões inteligentes ou de cartões inteligentes, não poderão mais ser usados. Além disso, a arquitetura do processador deve permanecer ágil e flexível – isso permite alterações nos algoritmos criptográficos devido a ameaças futuras sem a necessidade de substituição de hardware.

Além da eficiência e da compactação, a segurança física de uma implementação criptográfica também é importante. Os problemas matemáticos por trás de um algoritmo podem resistir a ataques conhecidos, mas as propriedades físicas de um computador, como flutuações de calor, radiação eletromagnética ou consumo de energia, também podem revelar informações confidenciais. Os invasores podem usar uma antena para descobrir o que está acontecendo em um dispositivo. A equipe de pesquisa desenvolveu, portanto, técnicas para proteger os sistemas contra tais ataques. Isto resultou na técnica de randomização de dados “Kavach”. Isso otimiza o esforço de computação usando propriedades numéricas especiais que são usadas nas operações de computação dos algoritmos. Os criptógrafos agora podem usar a técnica para desenvolver algoritmos pós-quânticos para KEM e assinaturas que são mais bem protegidas contra ataques baseados na física.

Passo importante para empresas e organizações

Vimos grandes saltos no campo dos processadores quânticos nos últimos cinco anos”, diz Sujoy Sinha Roy. “Quando computadores quânticos poderosos estiverem totalmente desenvolvidos, eles serão capazes de quebrar a criptografia em poucos segundos, o que levaria anos para computadores convencionais . Isto é perigoso para transações bancárias, sistemas de defesa governamentais e muito mais. Isto é muitas vezes referido como o apocalipse quântico e queremos evitá-lo. À medida que empresas e organizações se preparam para migrar para a criptografia pós-quântica, nossa pesquisa fornece outro passo importante rumo a essa transição.”

Este projeto foi financiado pela Semiconductor Research Corporation e está ancorado na Área de Atuação ” Informação, Comunicação e Computação “, um dos cinco campos científicos de força da TU Graz.